多闸极电晶体

多闸极电晶体(英语:Mulitgate Device)是指集合了多个闸极于一体的金属氧化物半导体场效电晶体(MOSFET)。它可以用一个电极来同时控制多个闸极,亦可用多个电极单独控制各闸极。后者有时又被叫做Multiple Independent Gate Field Effect Transistor(MIGFET)。多闸极电晶体被提出为的是克服半导体工业里摩尔定律(Moore's law)发展至今体积的缩小已经到达物理极限的难题。[1]

相当多的公司和机构已经在积极发展多闸极电晶体,其中包含了超微半导体、日立、IBM、英飞凌、英特尔、台积电、飞思卡尔、加州大学伯克利分校等等,而ITRS预估多闸极电晶体将是32奈米以下重要的奠基石。[2]实现上主要的障碍来自于制造技术,不论是平面和非平面的设计都面临挑战,特别是显影以及图案化技术。其他伴随发展的包含了通道应力、矽上绝缘(SOI)以及高介电质/金属闸极材料。

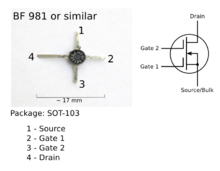

双闸极电晶体广泛用于超高频混频器(VHF mixers)和超高频前端放大器(VHF front end amplifiers)。制造商包含Motorola、NXP和Hitachi。[3][4][5]

工业需求[编辑]

平面电晶体主导了整个半导体工业已经好长一段时间。随著尺寸愈做愈小,出现了短通道效应,特别是漏电流,这类使得元件耗电的因素。

多闸极电晶体的载子通道受到接触各平面的闸极控制。因此提供了一个更好的方法可以控制漏电流。由于多闸极电晶体有更高的本征增益和更低的沟道调制效应,在类比电路领域也能够提供更好的效能。如此可以减少耗电量以及提升晶片效能。立体的设计也可以提高电晶体密度,进而发展需要高密度电晶体的微机电领域。

挑战[编辑]

如何将非平面电晶体相容于传统平面电晶体的制程所面临的挑战包含:

- 制造仅有10纳米左右的矽“鳍”

- 制造与矽鳍各面接触的合适闸极

变形[编辑]

文献里也有其他多种不同的设计。一般来说可分为平面和非平面,以及不同的通道和闸极数(2、3或4)。

平面双闸极电晶体[编辑]

平面双闸极电晶体使用传统平面(层层堆叠)的工艺过程来制造此双闸极元件,避免为了制造非平面、垂直的电晶体结构而必须引入更为复杂的显影设备。在平面双闸极电晶体里,源极/汲极通道像三明治一样被包裹在两个独立的氧堆叠闸极之间。建造这种结构的困难处在于如何让上下两个闸极能够自动地彼此对准。

FlexFET[编辑]

FlexFET是一种平面独立双闸极电晶体,它的上闸极部分是金属镶嵌闸极的MOSFET,下闸极部分则是深埋在闸极沟槽里且自对准的JFET。

FlexFET是一个真正的双闸极电晶体,其原因是(1)上下两个闸极都可对电晶体进行操作,以及(2)上下两个闸极的操作是彼此互相影响的。FlexFET正在发展当中且已经被美国半导体公司生产出来。

FinFET[编辑]

FinFET这词是由美国加州大学伯克利分校胡正明、刘金智洁(Tsu-Jae King-Liu)[6]、杰佛瑞·波克(Jeffrey Bokor)等3位教授所命名,用来描述一种基于早期DELTA(单闸极)电晶体的设计演化出来并建立在矽上绝缘基板上的非平面双闸极电晶体。FinFET主要的特色在于将导电通道包裹在矽“鳍”里面。源极和汲极之间的距离决定了这个元件的等效通道长度。

现在对FinFET这词的使用已经愈来愈模糊。微处理器厂商AMD、IBM、Motorola也把他们的双闸极元件叫做FinFET,而Intel却避免用这个词来称呼他们与此相像的三闸极电晶体。一般来说,FinFET被用在那些有“鳍”特征的电晶体上,并不在乎它确实有几个闸极存在。

2002年台积电制造出操作电压仅0.7伏特的25纳米电晶体。它的设计之后被命名为“Omega FinFET”,取自于它的闸极包裹住源极/汲极结构,其形状类似希腊字母omega(Ω)。对N型电晶体来说,它的闸极延迟仅有0.39皮秒(缩写ps),而对P型电晶体来说,仅有0.88ps。

FinFET可以设计成两个单独可控制闸极,这可以让电晶体的设计更为弹性,可以制造出更具效能、低耗电的元件。

2012年开始,Intel开始用FinFETs作为他们未来的商品。最近的消息透露,Intel的电晶体有不同于一般使用矩形的三角形结构,据推测是因为三角形比矩形有较高的结构强度,有助于提高制造的可靠度,而另一方面则是三角柱的面与体积的比例相对立方体来说来的大,这有助于提升开关性能。

2012年九月,GlobalFoundries宣布在2014年开始提供23纳米FinFET。隔一个月,它的竞争对手,台积电2013年11月开始生产16纳米FinFETs。

三闸极电晶体[编辑]

三闸极电晶体(Tri-gate)被Intel使用在自家的Ivy Bridge和Haswell处理器上。此元件将一个闸极堆叠在两个垂直放置的闸极上面,此电子多了三倍的可移动面积。Intel宣称他们的三闸极电晶体可以减少漏电流进而减少耗能。相对之前的产品而言,此元件可提高35%的速度并且仅需一半的耗电量。

Intel表示,"多出来的控制闸极允许我们在'开启'状态时尽可能增加电流量(以增进效能),和在'关闭'状态时让电流量趋近于零(减少耗能),并且可以让电晶体状态之间的转换速度变得更快(同样,可以增加效能)。Intel已经表明在Sandy Bridge之后的处理器都将基于此3D设计。

Intel是全世界第一个发表此项技术的厂商。在2002年九月,Intel宣称此元件"可最大化增加转换速度请减少耗电电流"。一年之后的2003年九月,AMD在一场国际固态元件和材料的研讨会上宣布他们也在做类似的设计。至此之后就没有其他消息,直至在2011年的英特尔开发者论坛(IDF 2011)上展示以他们在IDF2009年发表的技术制造的静态随机存取记忆体(SRAM chip)。

2012年4月23日,Intel建造了一个新的产线,命名为Ivy Bridge,主要生产三闸极电晶体。Intel自2002年就开始发展三闸极电晶体结构,但在2011年才正式量产。此种新型态电晶体在旧金山2011年4月4号被提出讨论。Intel产线端预计在2011年和2012年改良后可以开始生产Ivy Bridge中央处理器。除了在桌上型电脑内的Ivy Bridge中央处理器使用外,此元件也被使用在低功率的Atom晶片上。

"三闸极电晶体"一词有时也被广泛用来指在任何有三个有效闸极或通道的电晶体。

GAA FET[编辑]

闸极全环电晶体(Gate-all-around,GAAFET),或称为“环绕式结构FET”,和FinFET有相同的概念,不同之处在于此元件闸极围绕了整个载子通道。依设计的不同,GAAFET可以以2个或4个等效闸极。此元件已经藉著利用矽奈米线和蚀刻砷化镓铟(InGaAs)纳米线被建造成功。

简略模型[编辑]

UC Berkeley BSIM Group在2012年3月1号正式发表BSIMCMG106.0.0,这是第一个FinFET的标准模型。BSIM-CMG被实现在Verilog-A上。对于有限体参杂(body doping)的本质与非本质模型的物理面电势公式皆已被导出。考虑了多消耗以及量子效应的源极和汲极端的面电势也已明确地被导出来。透过微扰近似,我们已经可以理解有限体参杂的效应。导出的面电势也与2-D元件的模拟相当接近。如果通道的参杂浓度很低,低到可以忽略,那么在特殊情况下,我们可以更进一步改进计算效率。

所有重要的闸极电晶体的效应都已经被这个模型所捕捉。体积翻转效应被包含在泊松方程的解里,于是其后的I-V式子自然而然反映出了此效应。多闸极电晶体的电气准电势的分析给了如何解释短通道效应的模型。这个模型包含了如何去控制多馀的闸电极(上/下闸电极)。

参见[编辑]

注释[编辑]

- ^ Risch, L. "Pushing CMOS Beyond the Roadmap", Proceedings of ESSCIRC, 2005, p. 63.

- ^ Table39b (PDF). [2017-02-25]. (原始内容存档 (PDF)于2007-09-27).

- ^ 3N201 (Motorola) - Dual Gate Mosfet Vhf Amplifier. Doc.chipfind.ru. [2014-03-10]. (原始内容存档于2020-04-09).

- ^ 3SK45 datasheet pdf datenblatt - Hitachi Semiconductor - SILICON N-CHANNEL DUAL GATE MOSFET. Alldatasheet.com. [2014-03-10]. (原始内容存档于2020-04-09).

- ^ BF1217WR (PDF). [2015-05-10]. (原始内容 (PDF)存档于2020-04-09).

- ^ 劉金智潔 教授. 台湾科学特殊人才提升计画. [2023-01-28]. (原始内容存档于2023-01-28).